Ansteuerung und Abfrage der Pfeifenmagnete

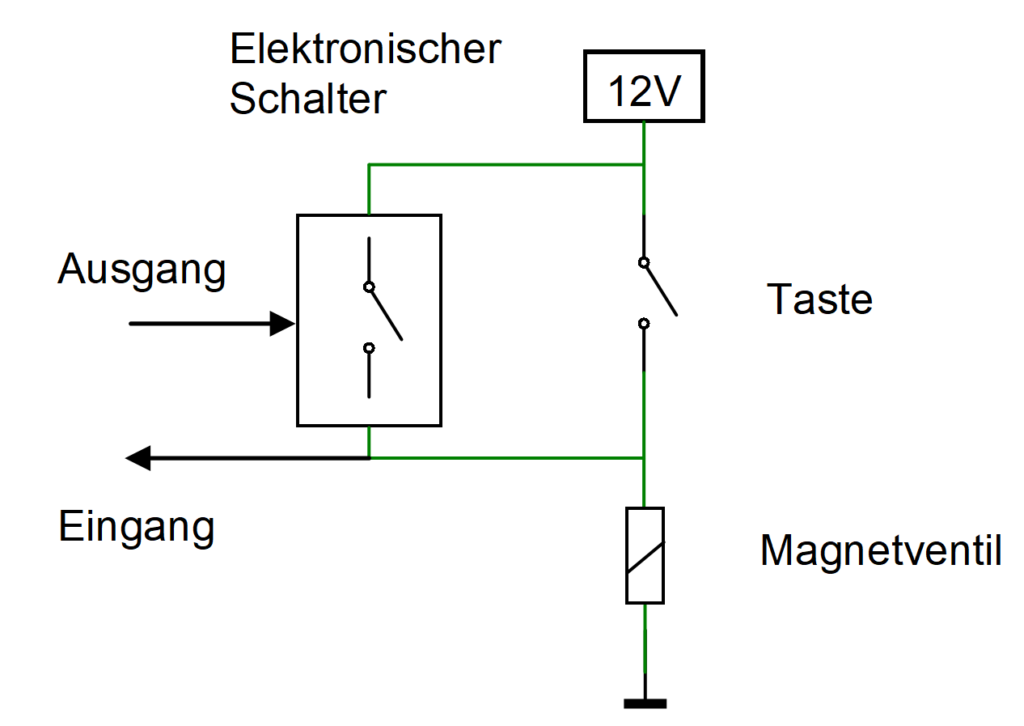

Für die Kirchenorgel sind 2 Ergänzungen der Funktionsweisen machbar. Ansteuerung der Pfeifen durch die Elektronik (z B. zur Realisierung eines MIDI-Eingangs) und Abfrage des Zustands der Tasten am Spieltisch (u. A. zur Weiterführung an den MIDI-Ausgang). Geschaltet und „gelesen“ werden müssen dabei die 12V, mit denen die Magnetventile gesteuert werden:

Schalten der 12V

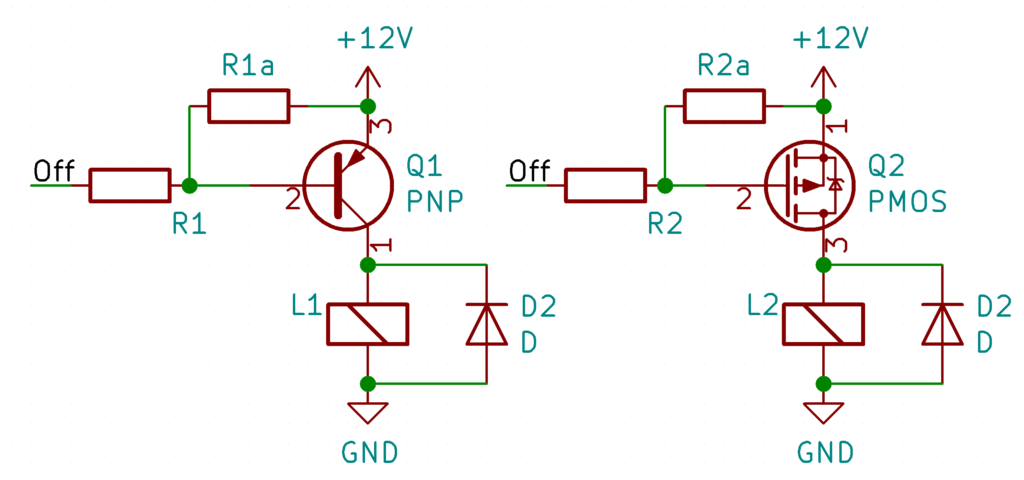

Das Schalten der 12V könnte durch PNP-Tranistoren oder P-Kanal-Mosfets erfolgen (1)(2):

Hier ist am Basiswiderstand R1 bzw. Gatewiderstand R2 ein 12V-Signal „Off“ nötig (12V=Transistor sperrt https://puttygen.in , 0V=Transistor leitet). Wegen der geringen Verluste habe ich mich für die MOSFETS entschieden.

Verwendet man diese Standard-Schaltungstechnik, so ist schon am Widerstand R1/R2 ein 12V Signal nötig oder ein Logikausgang, der nur gegen Masse („Gnd“) schaltet und unempfindlich für 12V ist (z.B. Open-Collector). Letzteres würde jedoch ein zusätzliches Bauteil bedeuten, da Ports oder Schieberegister mit solchen Ausgängen nicht verfügbar sind.

Es gäbe noch 2 Möglichkeiten, auf 12V in den Schaltkreisen für die Porterweiterung zu verzichten:

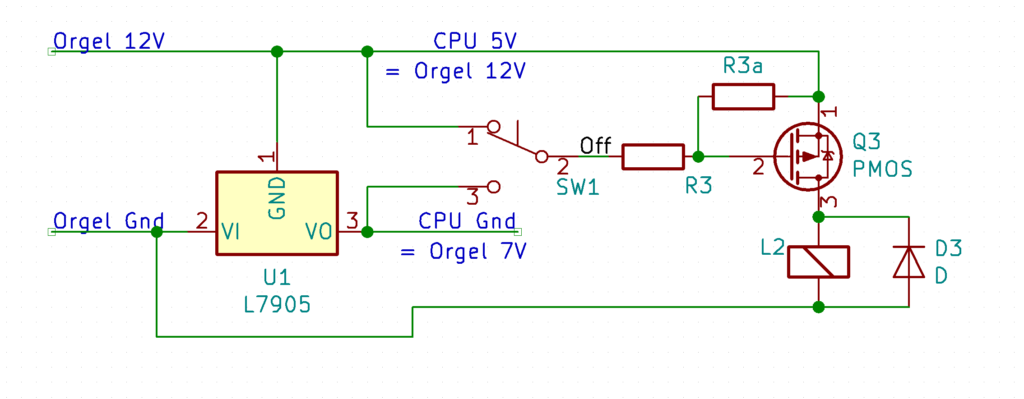

- Statt gemeinsame Masse von Orgel und Mikrocontroller gemeinsame Versorgungsspannung, dafür „Anhebung“ der Masse der Orgel auf die der CPU. Aus Zum Durchschalten der Transistoren würde die CPU Gnd = Orgel 7V ausreichen. (3)

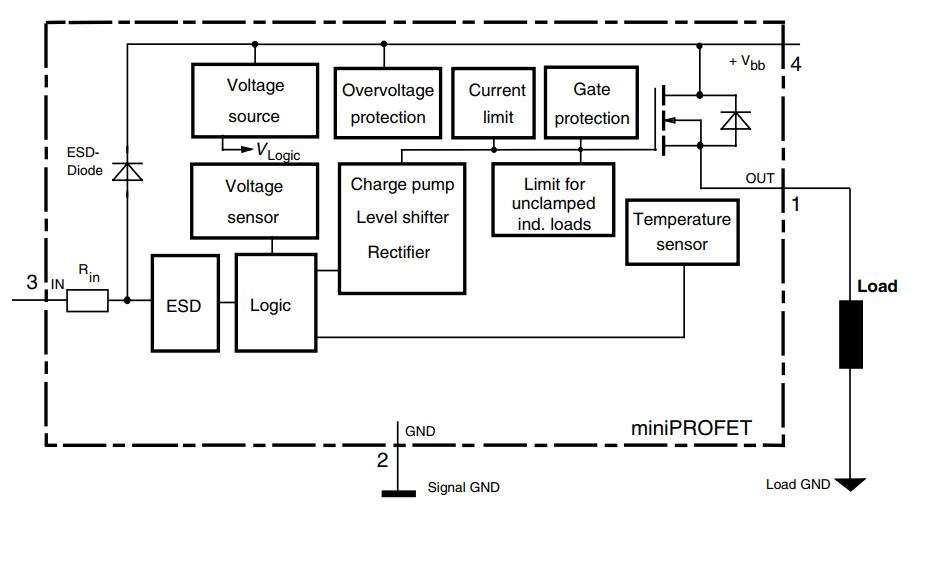

- Verwendungen von High-Side-Schaltern, die z.B. in der Automobiltechnik oft eingesetzt werden.

Zum Entwicklungszeitpunkt waren solche Schalter aber für Hobbyzwecke schwer erhältlich bzw. recht teuer. Daher habe ich mich gegen ihre Verwendung entscheiden. Rückblickend wäre jedoch der obige BSP 452 dafür gut geeignet. Dieser würde gegenüber der obigen Schaltung Transistor, Diode und 2 Widerstände einsparen und zudem die Sicherung, die oben nicht eingezeichnet ist. Ferner könnte alles mit 5V statt mit 12V betrieben werden. Die Eingangsschaltung müsste jedoch weiter 12V auf 5V reduzieren.

512 Port-Bits

256 Ein-/Ausgänge in 12V sind schon eine gewisse Herausforderung, zumal für Ein- und Ausgang jeweils getrennte Leitungen nötig sind. Kein normaler Mikrocontroller verfügt über so viele Ports. Ein Porterweiterung wäre möglich durch

- seriell angeschlossene Schieberegister (Vorteil: Einfach anzusteueren, leicht kaskasdierbar; Nachteil: Keine Fehlertoleranz im Protokoll)

- I2C Portbausteine (mittlerer Aufwand in Software, halbwegs robustes Protokoll)

- Slave-CPUs über SPI o.ä. (Vorteil: hohe Störsicherheit bei entsprechendem Protokoll, Nachteil: hoher Software-Aufwand, Extra Slave-System nötig)

Die Wandlung von 5V auf 12V scheint zunächst in jeder Variante gleich aufwändig zu sein; dies ist jedoch nicht der Fall: Die Schieberegister sind in können in der 4000er-CMOS-Ausführung direkt mit 12V betrieben werden, so dass nur die wenigen Schnittstellen-Leitungen zur CPU eine 5V-12V-Wandlung benötigen, statt der 256 Leitungen zur Ansteuerung der Transistoren. Dies war letztlich ausschlaggebend für die Entscheidung zugunsten der Schieberegister 4094.

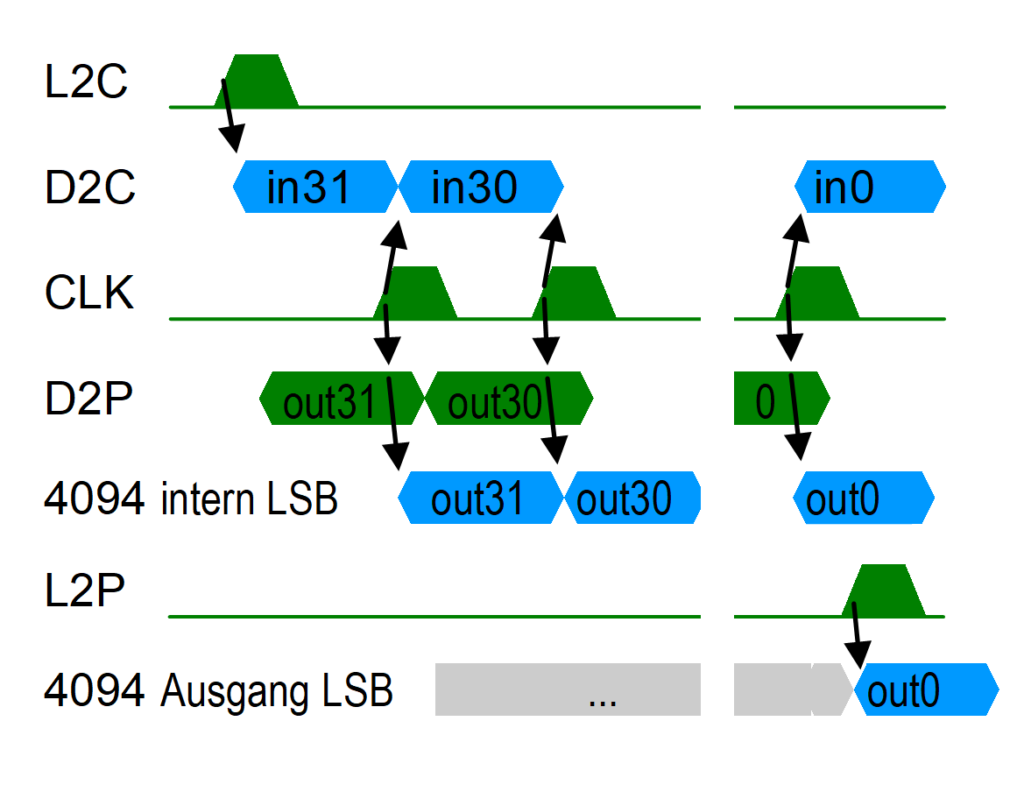

Die serielle Anordnung macht es nötig, immer alle Daten zu schreiben, nicht nur die, die sich geändert haben. Ebenso Die Taktrate soll 1 MHz nicht überschreiten, wegen der recht großflächigen Anordnung der vielen Platinen und den sich ergebenden Leitungslängen. Würde man alle 256 seriell übertragen, würde das 0,256 ms dauern (plus Software-Overhead), das wäre für die angestrebte Übertragung/Abfrage jede Millisekunde schon recht lang. Da die Schaltung zur Ansteuerung der 256 Leitungen sowieso auf mehrere Platinen (etwa 8) verteilt werden muss, war es nahe liegend, die Datenleitungen D2C (Lesen: Daten an CPU) und D2P (Schreiben: Ansteuerung der Transistoren durch die CPU) für jede Platine einzeln zu realisieren. So können 8 Bit in einem Taktzyklus parallel gelesen und geschrieben werden. Dadurch wird die Länge der seriellen Übertragung auf 32 Bit reduziert.

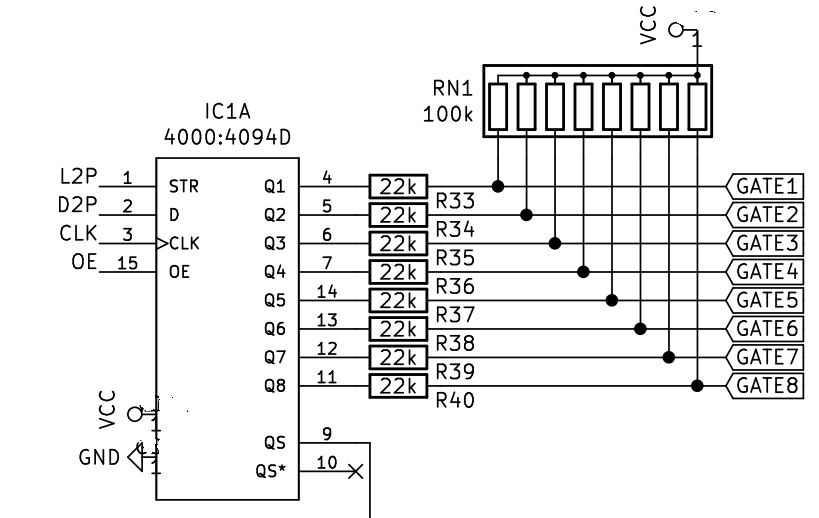

In den Eingang „D“ kommen über D2P die seriellen Daten von der CPU (beim ersten Schieberegister) bzw. vom vorherigen Schieberegister (Ausgang QS) bei den folgenden. Mit einer steigenden Flanke an CLK werden diese eingelesen. Sind alle Bits übertragen, so schreibt ein kurzer Impuls auf L2P die Daten in das Ausgansgregister, so dass diese auf Q1-Q8 erscheinen und die Transistoren über R33-40 ansteuern. OE schaltet die Ausgänge frei. Solange die Ansteuerung noch nicht arbeitet wird diese Leitung von der CPU auf Low gehalten

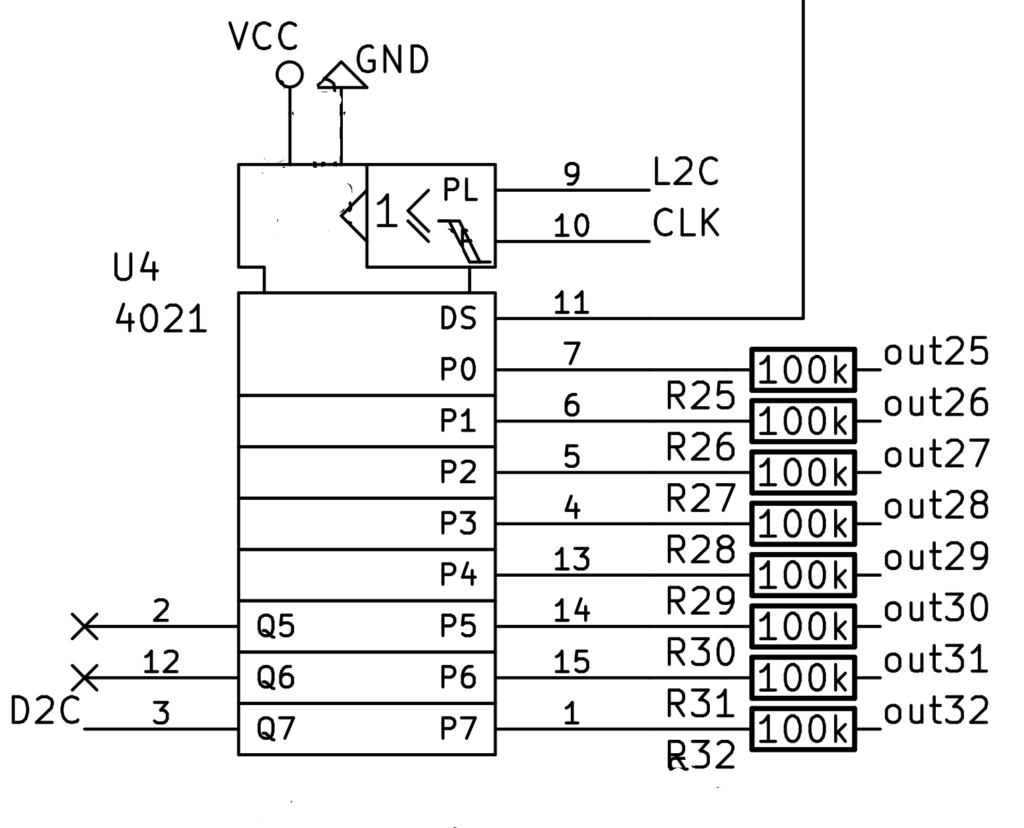

, so dass die Transistoren über RN1 gesperrt werden.Analog werden zum Lesen der Zustände der Tasten/Magnete Schieberegister 4021 verwendet (4):

Über R25-32 sind die parallelen Eingänge mit den Tasten/ Magneten/ Transistor-Ausgängen verbunden. Der aktuelle Status wird durch einen Impuls auf „L2C“ im Schieberegister gespeichert. Das oberste Bit (P7) erscheint an Q7 und wird an die CPU geführt („D2C“). Mit jedem Taktimpuls auf „CLK“ wird das nächste gespeicherte Bit an Q7 weitergeschoben. Über „DS“ wird Q7 vom vorherigen 4021 nachgeschoben (5).

Die Anzahl der Leitungen zum Datenaustausch wird dadurch verringert auf zweimal 8 für die Daten (Lesen und Schreiben finden ja gleichzeitig statt) und 4 für die Steuersignale L2C

, L2P, CLK und OE, also 20 Leitungen.Anmerkung

(1) Die Widerstände von Gate/Basis zu 12V sollen einen definierten Zustand sicherstellen

, wenn kein Signal anliegt.(2) Die Freilaufdioden sind zum Schalten der induktiven Last nötig.

(3) Orgel Gnd wäre dann aber aus Sicht der CPU -7V, was bei der Eingangsschaltung zu berücksichten wäre.

(4) Die Symbole für dieses IC stammen aus einer anderen Bibliothek, bei der die Bits 0…7 heißen, statt 1…8 wie beim 4094

(5) Am ersten 4021 wird QS des letzten 4094 über DS hineingeschoben. Somit erscheint nach dem 32. Taktimpuls das oberste der zuletzt in die 4094 geschrieben Bits am Lese-Ausgang D2C. Dadurch kann beim Selbsttest mit Testmustern geprüft werden, ob die Kette der Schieberegister in einem Modul funktioniert.

(6) Kleiner Fehler im Diagramm: Mit dem 31. CLK-Impuls erscheint das letzte Bit „in0“ des 4021 an D2C. Aber erst mit dem 32. CLK-Impuls wird das letzte zu schreibende Bit „out0“ in den 4094 übernommen